总线

总线

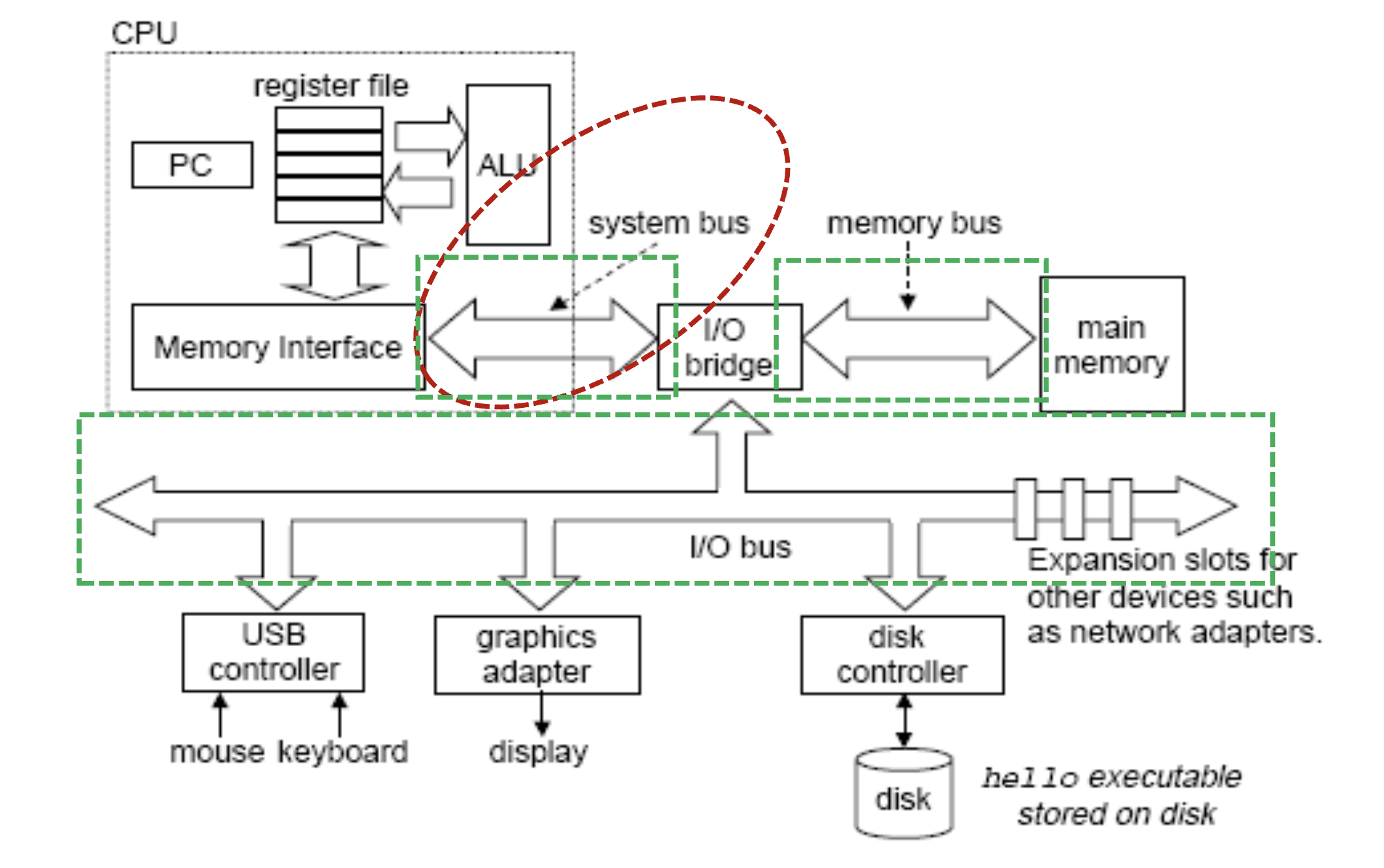

- 芯片内部总线:连接芯片内部的各个部分

- 例:CPU中连接寄存器、ALU等部分

- 系统总线:连接CPU、存储器、IO控制器和其他功能设备

- 通信总线:连接主机和I/O设备,或连接不同的计算机系统

数据线:在系统组件之间传输数据,数据线的数量决定了一次可以传输的数据的大小

地址线:在数据线和地址I/O端口上指定数据的来源和去向,地址线的数量决定了寻址空间的大小

总线上数据传输的特点

- 总线可以被多个设备监听,但同一时刻只能由一个设备发送数据。如果同一时刻多个设备同时发送数据,会造成数据之间的混淆

- 使用总线进行数据传输

- 如果连在总线上的某个设备希望向另一个设备发送数据,需要:

- 获得总线的使用权

- 通过总线传送数据

- 如果连在总线上的某个设备希望向另一个组件请求数据,需要:

- 获得总线的使用权

- 通过总线向另一个设备发送请求,等待另一个设备发送数据

- 如果连在总线上的某个设备希望向另一个设备发送数据,需要:

- 当总线在被使用过程中,其它设备不可以抢占

用途

- 专用(dedicated)总线:始终只负责一项功能,或始终分配给特定的计算机组件

- 优点:高吞吐量,减少总线冲突

- 缺点:增加了系统的规模和成本

- 复用(multiplexed)总线:将同一线路用于多种用途

- 优点:使用的布线数量少,节省空间和成本

- 缺点:每个模块需要更复杂的控制电路,且共享可能会降低性能

仲裁

总线仲裁:当多个设备需要与总线通信时,通过某种策略选择一个设备

平衡因素:

- 优先级:优先级高的设备优先被服务

- 公平性:优先级最低的设备不能一致被延迟

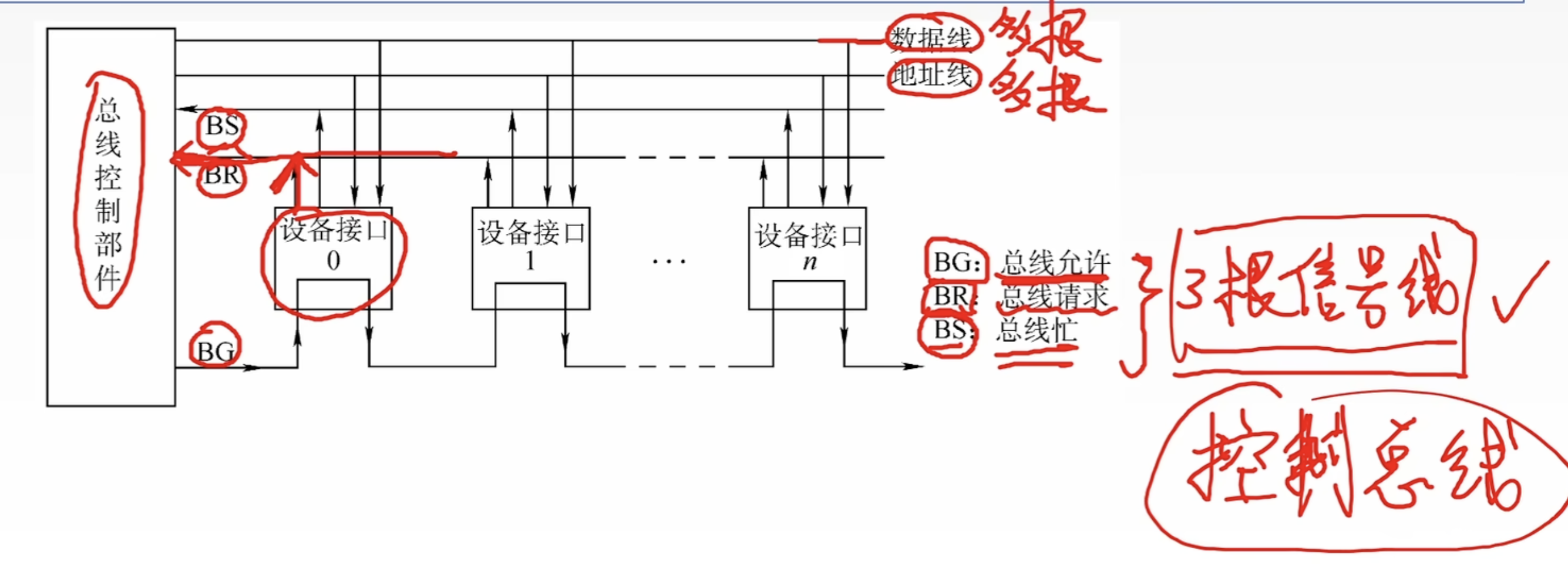

集中式仲裁

- 由仲裁器(arbiter)或总线控制器(bus controller)负责分配总线使用权

- 信号线:硬件读取信号线上的信号获知总线状态

- BG/允许线:仲裁器->设备,表明设备正被授权使用总线,每个设备有独立的BG信号

- BR/请求线:设备->仲裁器,表明需要使用总线

- BS/繁忙线

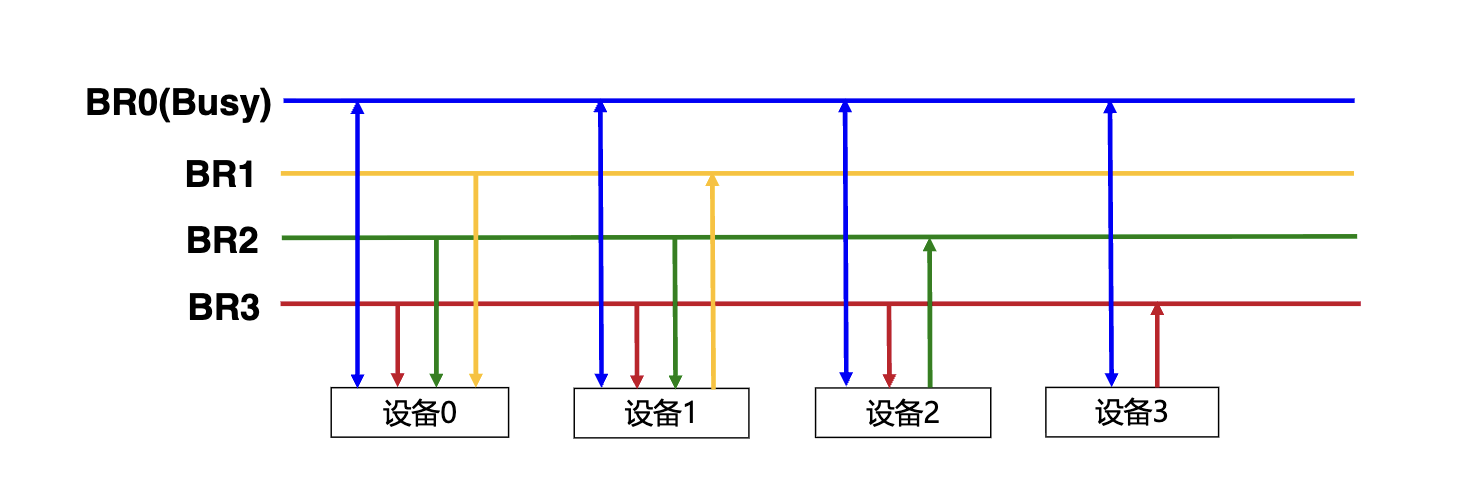

链式查询 Daisy chain

- 设备串行连接

- 允许信号从高优先级设备下发到低优先级设备

- 仲裁器收到请求后,在总线不忙的前提下发起允许信号

- 若设备收到允许信号并发起总线请求,设备将总线设置为繁忙状态,允许信号不再进一步传递

- 优点

- 确定优先级很简单

- 可灵活添加设备

- 缺点

- 不能保证公平性:远端设备无法及时访问

- 对电路故障敏感(链式)

- 限制总线速度

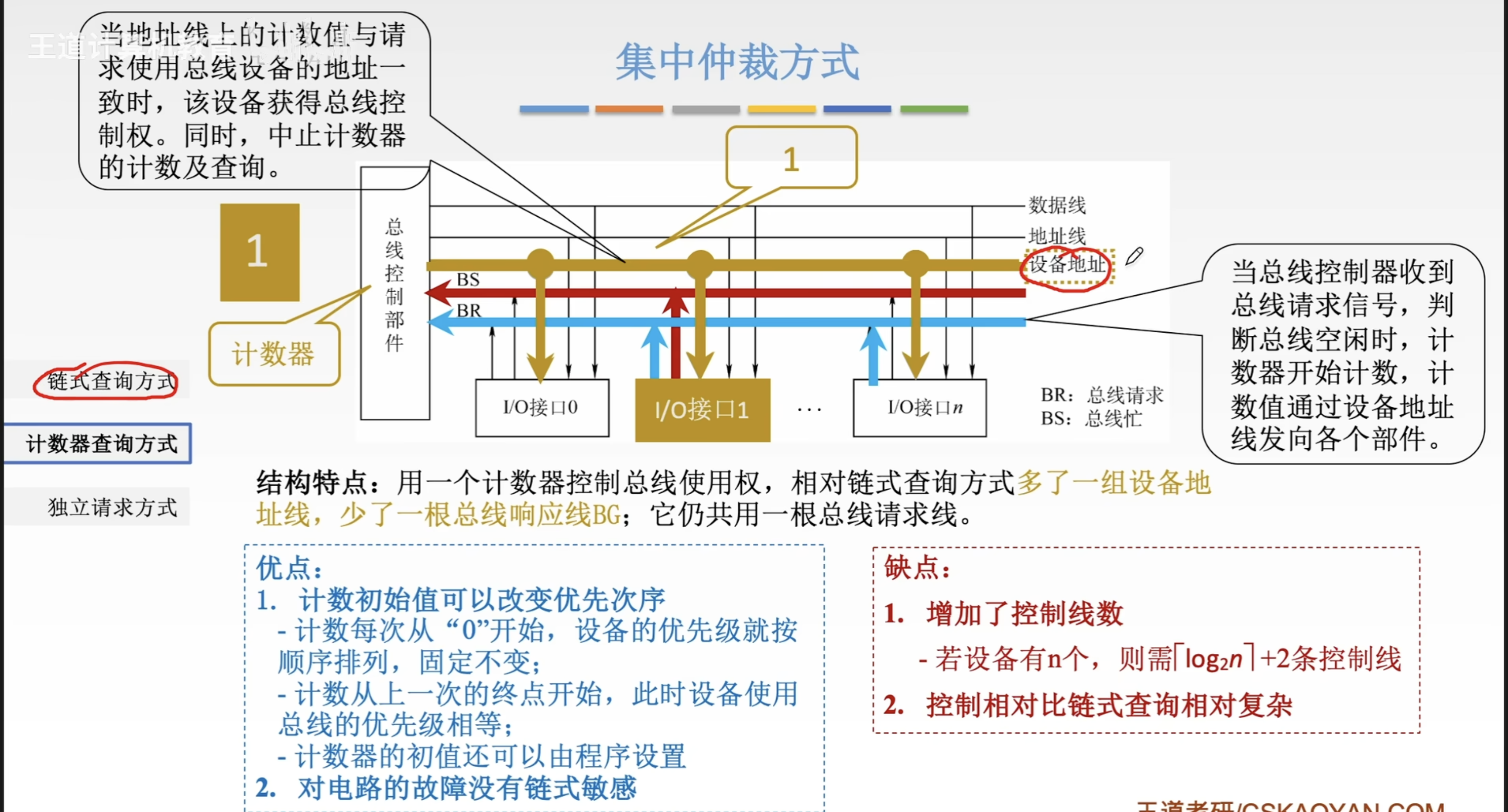

计数器查询

- 将允许线替换为ID线

- 总线空闲时,仲裁器通过ID线发送计数

- 若发送请求的设备ID=裁决器当前的计数,裁决器停止计数,设备总线设置为忙

- 优点

- 可通过不通的初始计数灵活确定设备优先级

- 强调优先级:从1开始

- 强调公平性:从下一个设备的ID开始

- 对电路故障不敏感

- 可通过不通的初始计数灵活确定设备优先级

- 缺点

- 需要添加设备ID线

- 需要解码、比较ID信号

- 限制总线的速度

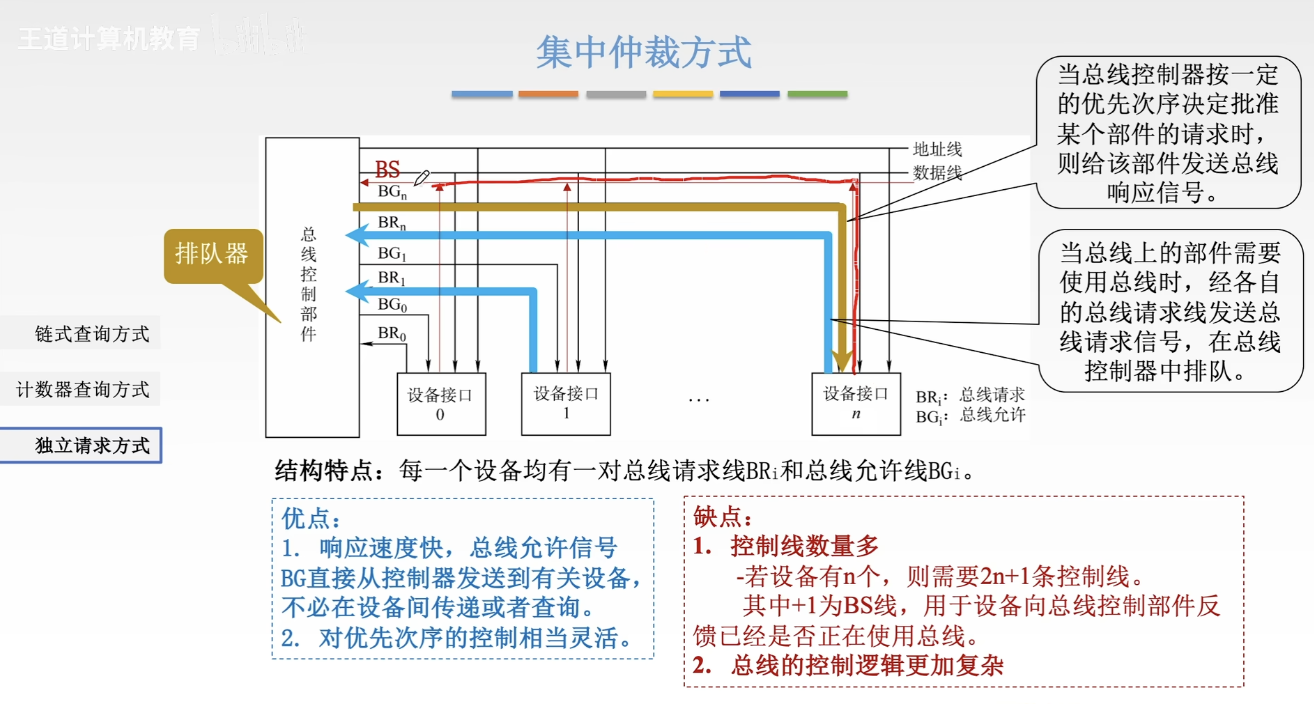

独立请求

- 繁忙线共享、允许线和请求线独立

- 当设备请求总线时通过请求线发送信号给仲裁器

- 仲裁器决定优先级(固定/链式/LRU/FIFO……)

- 优点

- 快速响应

- 优先级可编程

- 缺点

- 控制逻辑复杂

- 控制线路更多

分布式仲裁

- 每个设备都包含访问控制逻辑,各个设备共同作用分享总线

自举式

- 优先级固定

- 需请求总线的设备在对应的总线请求线上发送信号

- 若使用总线时,设备需分析BR0和比自己优先级更高的设备的请求线(接入的请求线)的信号,当全部空闲时才能使用

- 最低级的设备无需请求线,因为没有其他设备需以此为依据去判断

- N条设备N条请求线

- 上图中优先级3>2>1>0

冲突检测

- 当设备想要使用总线时检测总线是否繁忙,不繁忙即发送

- 同时使用产生冲突时:

- 在传输设备时监听总线检查是否冲突

- 若冲突立即停止传输,在随机间隔时间后再次请求

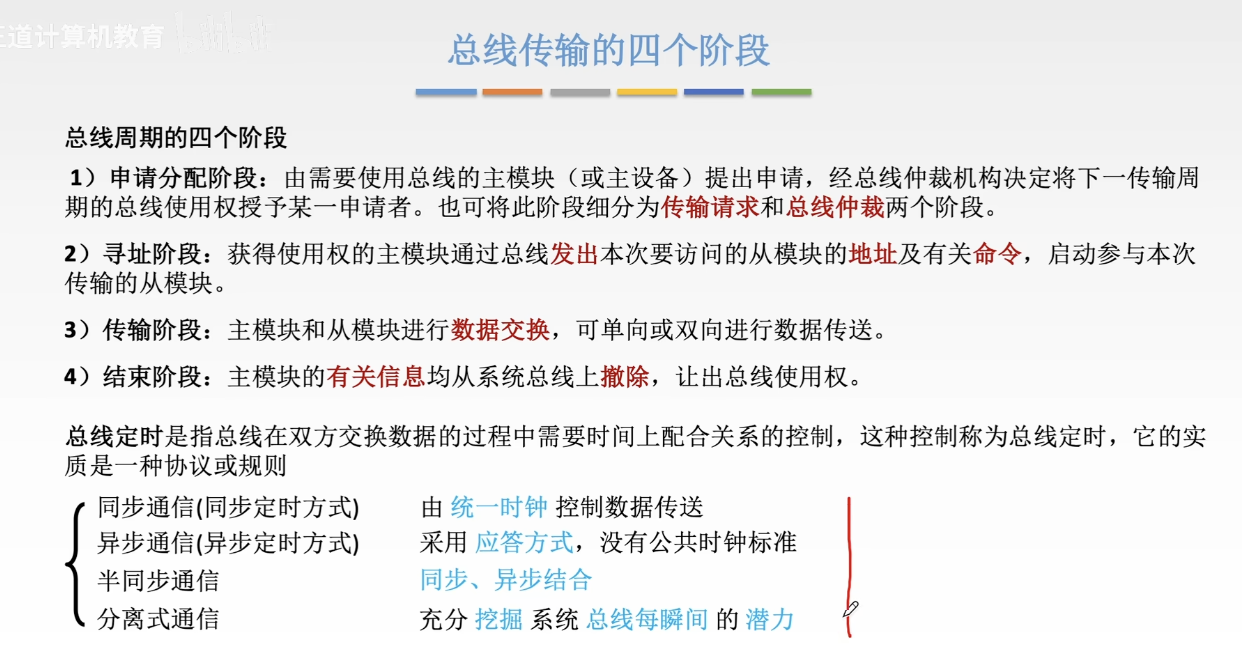

时序

- 确认总线事务的起止时间

- 总线事务:地址+数据+数据+……+数据

同步时序

- 事件的发生由时钟决定

- 总线包含时钟线,定时发送规则的0/1信号

- 时间在时钟周期开始时发生

- 优点:更易实现,测试

- 缺点

- 所有设备共享一个时钟,存在瓶颈

- 总线长度受到时钟偏差限制

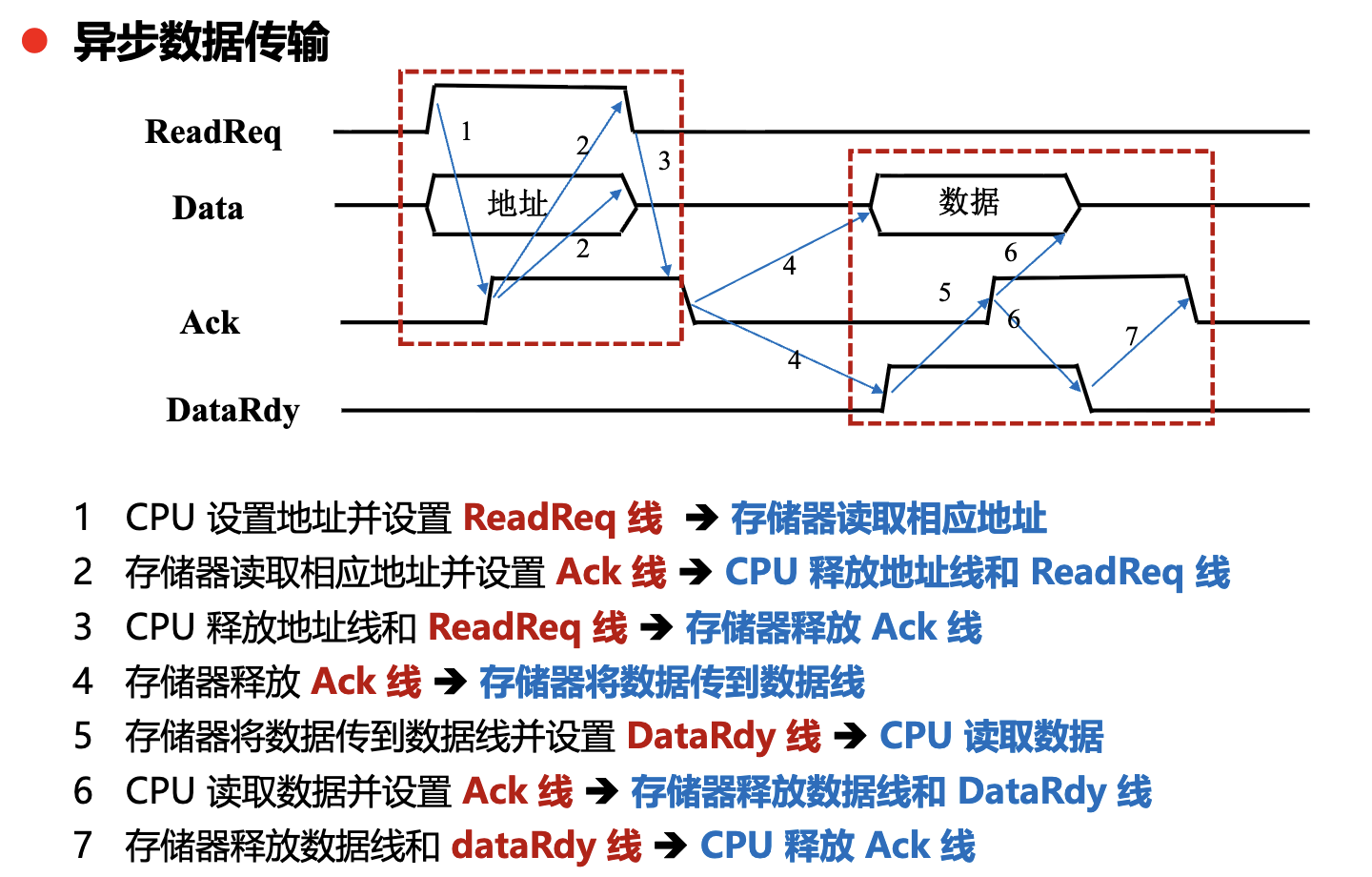

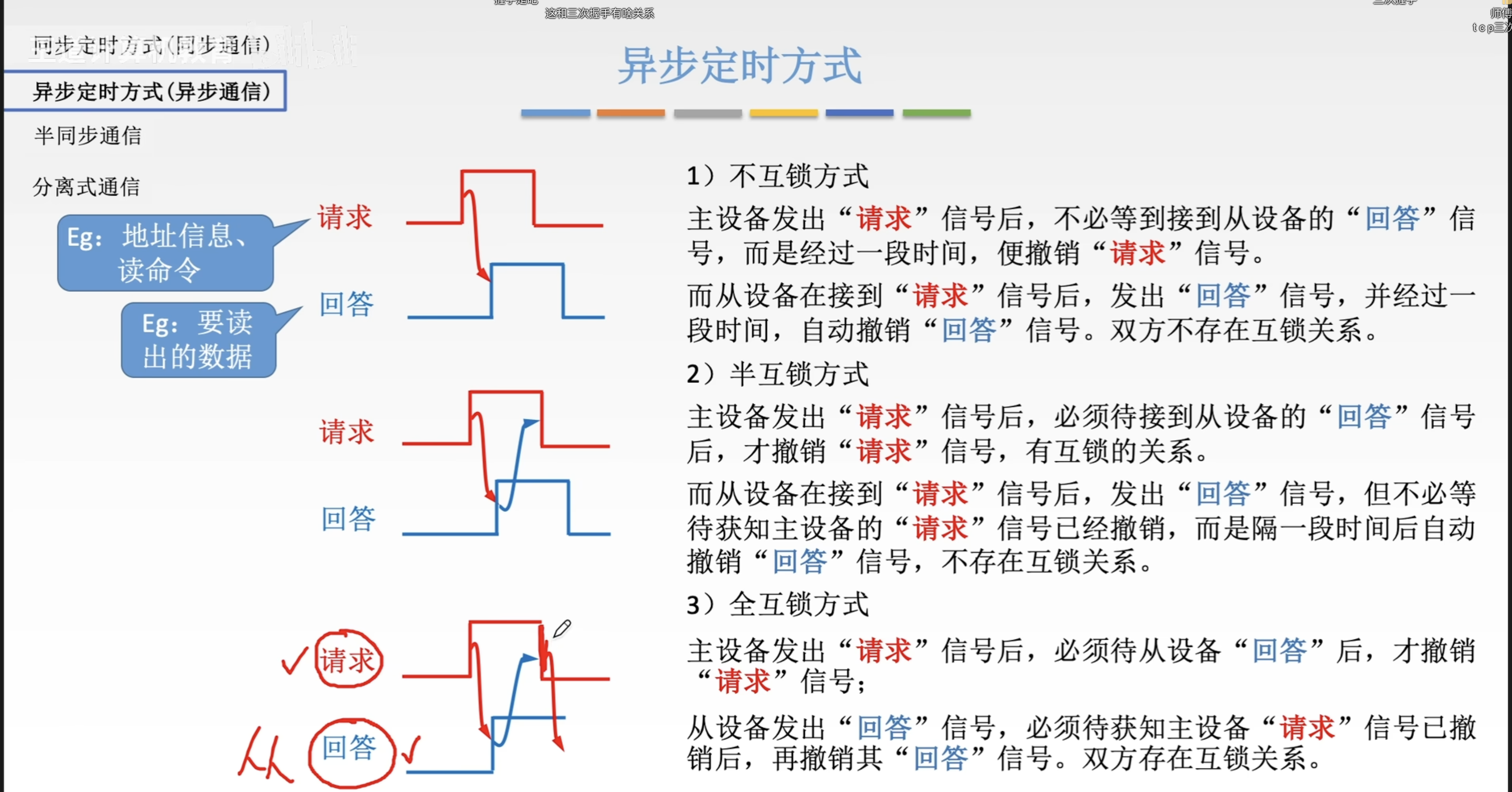

异步时序

- 事件的发生取决于前一事件的发生(握手信号)

- 采用握手协议,双方都同意时才会继续

- 非互锁/半互锁/全互锁

- 优点:可灵活协调不同设备

- 缺点

- 逻辑复杂

- 对噪声敏感

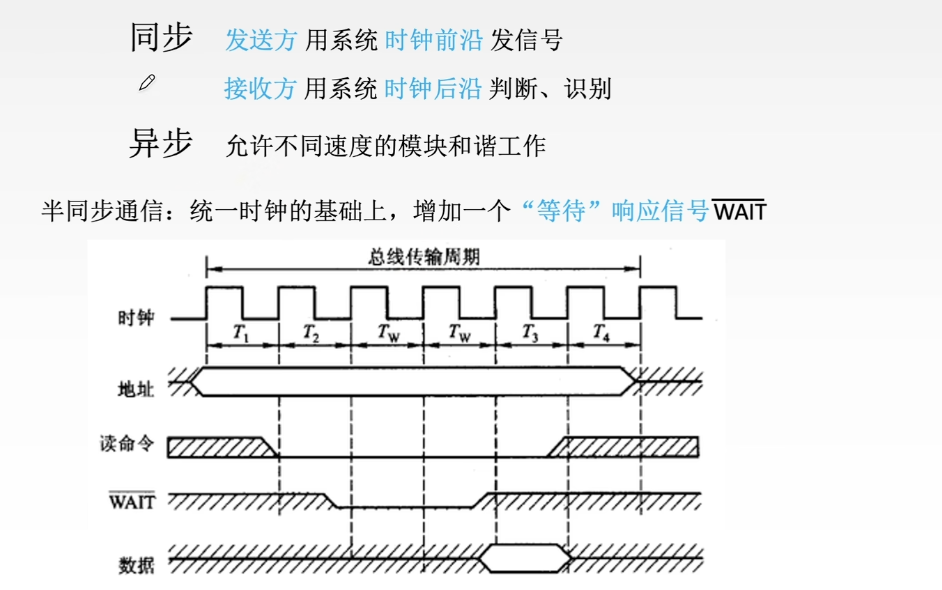

半同步

- 同步+异步

- 在异步时序中引入时钟以减少噪声,准备和响应信号只在时针上升沿有效

- 结合二者优点

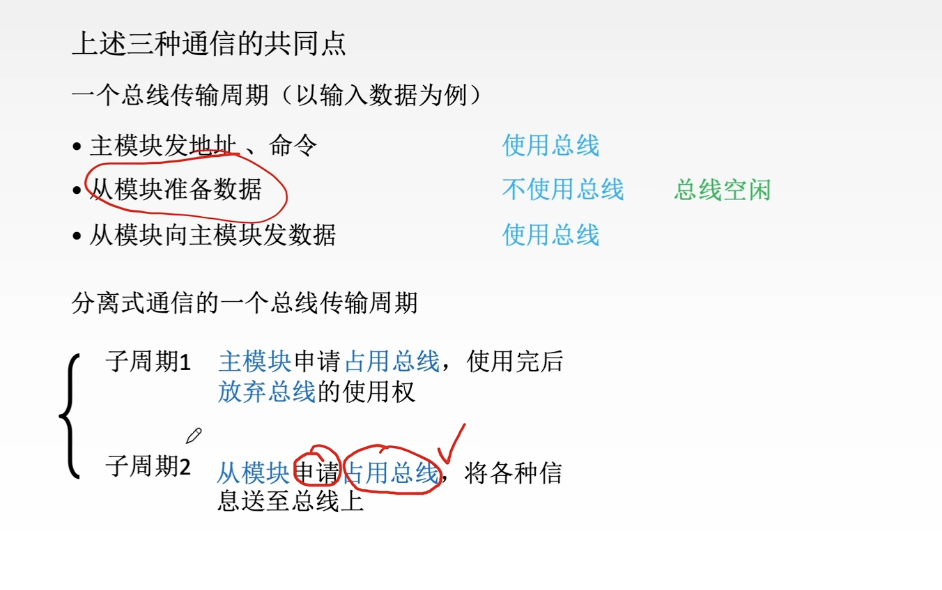

分离事务

- A请求B和B回复A之间存在空闲时间,在设备准备数据期间释放总线

- 优点:增加总线利用率

- 缺点:增加总线时间的持续时间和系统复杂度

速率指标

- 总线带宽:最大传输速率,不考虑仲裁、握手、地址传输

- 数据传输速率:考虑仲裁、握手、地址传输等因素

- 总线宽度:组成总线的线数

总线层次结构

单总线结构

- CPU/存储器/IO模块都连接到一条系统总线

- 优点:简单、易于扩展

- 缺点

- 连接设备越多,总线长度越大,延迟越大

- 传输请求增加后总线容量存在瓶颈

双总线结构 I

- 在CPU和存储器单独增加存储器总线

- 优点:降低系统总线负担,增加CPU和主存的传输效率

双总线结构 II

- 单独拆分I/O,将系统总线分为:存储器总线、IO总线、IOP

- 优点:降低I/O对总线的负担

多总线结构 I

- 增加本地总线连接CPU和Cache

- 优点:分离CPU和I/O的交互

多总线结构 II

- 将系统总线分为存储器总线、I/O 总线和 DMA 总线

- 优点:增加I/O效率

多总线结构 III

- 增加高速I/O总线连接高速设备

- 优点:增加I/O交互效率

This post is licensed under CC BY 4.0 by the author.